Базовая версия MCS–51 Краткие сведения. Современные 8–разрядные микроконтроллеры (МК) обладают такими ресурсами управления в режиме реального времени, для получения которых раньше использовались дорогие многокристальные компоновки в виде отдельных плат микроЭВМ, A именно:

● имеют достаточную емкость памяти, физическое и логическое ее разделение на память программ и память данных (гарвардскую архитектуру) и систему команд, ориентированную на выполнение алгоритмов управления;

● включают в себя все устройства (процессор, ПЗУ, ОЗУ, порты ввода–вывода, систему прерываний, средства обработки битовой информации и др.), необходимые для реализации микропроцессорной системы управления минимальной конфигурации. В 70–е годы прошлого столетия фирмой Intel разработан и освоен промышленный выпуск семейства 8–разрядных микроконтроллеров MCS–48, объединенных рядом общих признаков (разрядностью, системой команд, набором основных функциональных блоков и др.). Базовая версия этого семейства включает в себя:

● 8–разрядный процессор;

● внутреннюю память программ (1/2/4К байт);

● внутреннюю память данных (64/128/256 байт);

● до 27 внутренних и 16 внешних линий ввода–вывода;

● один 8–разрядный таймер–счетчик;

● одноуровневую систему прерываний с двумя источниками запросов. В 1980 г. той же фирмой было разработано новое семейство восьмиразрядных микроконтроллеров MCS–51, которое совместимо с архитектурой семейства MCS–48, но обладает более широкими возможностями.

Архитектура семейства MCS–51 оказалась настолько удачной, что и по настоящее время является одним из стандартов 8–разрядных МК. Поэтому объектом изучения выбраны МК этого семейства, получившие широкое распространение в сравнительно простых системах управления.

Для семейства MCS–51 разработаны различные средства подготовки программ (компиляторы, аппаратно–программные эмуляторы и др.) и имеется большое число библиотек стандартных подпрограмм. В состав семейства входят разнообразные модификации микросхем (версии кристаллов) микроконтроллеров. В статьях этого раздела достаточно подробно рассматривается базовая версия микроконтроллеров семейства MCS–51 (микросхеме 8051 соответствует отечественный аналог КP1816ВЕ51), наиболее простая в структурно–функциональном плане и с точки зрения понимания.

Последующие серии микросхем, сохраняя совместимость с базовой версией, отличаются от нее улучшенной технологией изготовления, электрическими параметрами, дополнительными аппаратными средствами и функциональными возможностями. Структурно–функциональным особенностям последующих модификаций микросхем семейства MCS–51 посвящены следующие статьи.  Обобщенная структурная схема MCS–51. В состав МК, обобщенная структурная схема которого приведена на рис. 7.1.1, входят:

Обобщенная структурная схема MCS–51. В состав МК, обобщенная структурная схема которого приведена на рис. 7.1.1, входят:

● 8–разрядный центральный процессор ЦП, состоящий из АЛУ , устройства управления УУ и формирователя адреса ФА ;

● масочное ПЗУ емкостью 4К байта для хранения программ;

● ОЗУ емкостью 128 байт для хранения данных;

● четыре программируемых порта Р0–Р3 для ввода–вывода информации;

● блок последовательного интерфейса БПИ для обмена информацией с внешними устройствами по двухпроводной линии;

● блок таймеров/счетчиков БT/C для поддержания режима реального времени;

● блок прерываний БП для организации прерываний исполняемых программ. Эти средства образуют резидентную часть микроконтроллера, размещенную непосредственно на кристалле. В состав МК входит большое число регистров, которые отнесены к отдельным функциональным блокам и на схеме не показаны.

На схеме также не показаны цепи управления. Двусторонний обмен информацией между блоками осуществляется по внутренней 8–разрядной шине данных ШД–8.

По внутренней 16–разрядной шине адреса ША–16 сформированный в ЦП адрес выводится в ПЗУ (12 разрядов адреса) и в ОЗУ (8 младших разрядов).

При использовании внешней памяти в порт Р0 выводятся 8 младших разрядов адреса и в порт P2 - 3 или 8 старших разрядов.

Для логического расширения интерфейса используется совмещение функций линий портов. В качестве примера на рис. 7.1.1 пунктиром показаны линии порта Р3, выполняющие альтернативные

функции передачи управляющих сигналов, о назначении которых будет сказано ниже. Для создания внутреннего тактового генератора к выводам микросхемы МК подключаются кварцевый резонатор и два конденсатора (рис. 7.1.1). Вместо внутреннего тактового генератора для синхронизации можно использовать внешний источник колебаний. Условное графическое обозначение микросхемы МК приведено на рис. 7.1.2, обозначение и назначение выводов - в табл. 7.1.1. Рассмотрим функциональные блоки МК и принцип их работы.  Арифметическо–логическое устройство. Арифметическо–логическое устройство предназначено для выполнения арифметических (включая умножение и деление) и логических операций над восьмиразрядными операндами, A также операций логического сдвига, обнуления, установки и др. Структурная схема АЛУ приведена на рис. 7.1.3.

Арифметическо–логическое устройство. Арифметическо–логическое устройство предназначено для выполнения арифметических (включая умножение и деление) и логических операций над восьмиразрядными операндами, A также операций логического сдвига, обнуления, установки и др. Структурная схема АЛУ приведена на рис. 7.1.3.

В состав АЛУ входят

● параллельный восьмиразрядный сумматор SМ комбинационного типа с последовательным переносом, выполняющий арифметические (сложение и вычитание) и логические (сложение, умножение, неравнозначность и тождественность) операции;

● аккумулятор A, обеспечивающий функции основного арифметического регистра;

● регистр В, используемый для реализации операций умножения и деления или как дополнительный сверхоперативный регистр, функции которого определяет пользователь;

●регистры (программно недоступные) временного хранения РВХ1, РВХ2, предназначенные для приема и хранения операндов на время выполнения операции;

● ПЗУ констант ПЗУК, хранящее корректирующий код для двоично–десятичного представления данных, код маски при битовых операциях и код констант;

● регистр слова состояния программы

PSW, фиксирующий состояние АЛУ после выполненной операции. В табл. 7.1.2 приведены сведения о назначении битов отдельных разрядов регистра PSW. Устройство управления. Устройство управления (УУ) центрального процессора предназначено

для координации совместной работы всех узлов МК с помощью вырабатываемых синхроимпульсов и управляющих сигналов. В его состав входят (рис. 7.1.4):

● узел синхронизации и управления УСУ, который формирует синхроимпульсы, задающие машинные циклы и их отдельные состояния (S) и фазы (Р), и в зависимости от режима работы МК вырабатывает необходимый набор управляющих сигналов. На выполнение команды отводится один, два или четыре машинных цикла.

Каждый машинный цикл имеет шесть состояний S1–S6, A каждое состояние включает в себя две фазы P1, P2, длительность которых составляет период колебаний тактового генератора T 0SC .

Длительность машинного цикла равна 12T 0SC . Все машинные циклы одинаковые, начинаются с фазы S1P1 и заканчиваются фазой S6P2.

Помимо синхроимпульсов устройство синхронизации в каждом машинном цикле формирует два (иногда один) сигнала стробирования младшего байта адреса ALE в виде положительного импульса в фазах S1P2–S2P1 и S4P2–S5P1. Временные диаграммы на рис. 7.1.5 иллюстрируют организацию машинных циклов;

● регистр команд РК, дешифратор команд ДК и ПЛМ, позволяющие в каждом машинном цикле сформировать набор микроопераций в соответствии с микропрограммой выполняемой команды;

● логика ввода–вывода ЛВВ для приема и выдачи сигналов, обеспечивающих обмен информацией МК с внешними устройствами через порты Р0–Р3;

● регистр PCON, имеющий единственный задействованный бит SMOD в позиции PCON.7 для удвоения скорости передачи данных через последовательный порт. Остальные биты зарезервированы для дальнейшего использования.  Формирователь адреса. Формирователь адреса (ФА), или счетчик команд РС, предназначен

для формирования текущего 16–разрядного адреса программной памяти и 8/16–разрядного адреса внешней памяти данных. В его состав входят (рис. 7.1.6):

Формирователь адреса. Формирователь адреса (ФА), или счетчик команд РС, предназначен

для формирования текущего 16–разрядного адреса программной памяти и 8/16–разрядного адреса внешней памяти данных. В его состав входят (рис. 7.1.6):

● 16–разрядный буфер Б, осуществляющий связь между 8–разрядной шиной данных ШД и 16–разрядной внутренней шиной (ВШ) формирователя адреса;

● схема инкремента СИ для увеличения значения текущего адреса памяти программ на единицу;

● регистр для хранения текущего адреса команд РТА, поступающего из СИ;

● регистр указателя данных DPTR, состоящий из двух 8–разрядных регистров DPHи DPL. Он служит для хранения 16–разрядного адреса внешней памяти данных и может быть использован в качестве двух независимых программно доступных РОН;

● регистр формирователя адреса РФА для хранения исполнительного 16–разрядного адреса памяти программ или 8/16–разрядного адреса внешней памяти данных. Этот регистр используется также для передачи данных через порт Р0 во внешние устройства при выполнении команд MOVX @Rm, A и MOVX @DPRT, A.

Память данных. Память данных предназначена

для приема, хранения и выдачи информации, используемой в процессе выполнения программы. Внутренняя (резидентная) память (рис. 7.1.7) данных состоит из ОЗУ емкостью 128 байт, указателя стека

SP, регистра адреса

ОЗУ РА и дешифратора

Дш.  Указатель стека SP представляет собой 8–разрядный регистр, предназначенный для приема и хранения адреса ячейки стека, к которой было последнее обращение. После сброса в указателе стека устанавливается адрес 07Н, что соответствует началу стека с адресом 08Н. Регистр адреса РА совместно с дешифратором Дш позволяет осуществить доступ к требуемой ячейке памяти, содержащей байт или бит информации.

Указатель стека SP представляет собой 8–разрядный регистр, предназначенный для приема и хранения адреса ячейки стека, к которой было последнее обращение. После сброса в указателе стека устанавливается адрес 07Н, что соответствует началу стека с адресом 08Н. Регистр адреса РА совместно с дешифратором Дш позволяет осуществить доступ к требуемой ячейке памяти, содержащей байт или бит информации.

В МК предусмотрена возможность увеличения объема памяти данных до 64 Кбайт путем подключения внешних запоминающих устройств.

В качестве примера на рис. 7.1.8 показана страничная организация внешней памяти данных ВПД емкостью 2К байт с использованием команд типа MOVX @

Rm(m = 0; 1). При этом порт Р0 работает как мультиплексированная шина адрес/данные, три линии порта P2 используются для адресации страницы внешнего ОЗУ, A остальные пять линий могут быть задействованы в качестве линий ввода–вывода.  На рис. 7.1.9 приведены временные диаграммы циклов чтения и записи при работе МК с внешним ОЗУ. На диаграммах обозначено:

На рис. 7.1.9 приведены временные диаграммы циклов чтения и записи при работе МК с внешним ОЗУ. На диаграммах обозначено:

● РСН - старший байт счетчика команд PC;

● DPL, DPH - младший и старший байты регистра указателя данных DPTR, который используется в качестве регистра для косвенной адресации в командах MOVX @DPTR,A и MOVX A,@DPTR;

● P2 SFR - защелки порта P2;

● Rm (m = 0, 1) - регистры, используемые в командах MOVX @Rm, A и MOVX A, @Rm в качестве регистров косвенного адреса;

● Z - высокоомное состояние;

● D - период, в течение которого данные из порта Р0 вводятся в микроконтроллер.  Память программ. Память программ предназначена для хранения программ, имеет свое (отдельно от памяти данных) адресное пространство и доступна только для чтения. В ее состав входит дешифратор Дш и ПЗУ (рис. 7.1.10).

Память программ. Память программ предназначена для хранения программ, имеет свое (отдельно от памяти данных) адресное пространство и доступна только для чтения. В ее состав входит дешифратор Дш и ПЗУ (рис. 7.1.10).  Для адресации памяти программ используется 16–разрядный счетчик РС, поэтому ее максимальная емкость составляет 64К байта. Внутренняя память программ состоит из ПЗУ емкостью 4К байт и 12–разрядного дешифратора. Внешняя память подключается по схеме на рис. 7.1.11.

Для адресации памяти программ используется 16–разрядный счетчик РС, поэтому ее максимальная емкость составляет 64К байта. Внутренняя память программ состоит из ПЗУ емкостью 4К байт и 12–разрядного дешифратора. Внешняя память подключается по схеме на рис. 7.1.11.  Если на вывод ¯EA МК подается 0 В (как показано на рис. 7.1.11), внутренняя память программ отключается. Все обращения к памяти начинаются с адреса 0000h. При подключении вывода ¯ЕА к источнику питания обращение к внутренней памяти программ по адресам 0000h–FFFFh и к внешней памяти программ по адресам 0FFFh–FFFFhпроисходит автоматически.

Если на вывод ¯EA МК подается 0 В (как показано на рис. 7.1.11), внутренняя память программ отключается. Все обращения к памяти начинаются с адреса 0000h. При подключении вывода ¯ЕА к источнику питания обращение к внутренней памяти программ по адресам 0000h–FFFFh и к внешней памяти программ по адресам 0FFFh–FFFFhпроисходит автоматически.

Для чтения внешней памяти программ МК вырабатывается сигнал ¯PSEN. При работе с внутренней памятью сигнал чтения не используется. При обращениях к внешней памяти программ всегда формируется 16–разрядный адрес. Младший байт адреса передается через порт Р0 в первой половине машинного цикла и фиксируется по срезу строба АLЕ в регистре Во второй половине цикла порт Р0 используется для ввода в МК байта данных из внешней памяти.

Старший байт адреса передается через порт P2 в течение всего времени обращения к памяти.

Временные диаграммы циклов чтения и записи при работе МК с внешним ОЗУ приведены на рис. 7.1.12.  На диаграммах обозначено:

На диаграммах обозначено:

● PCL OUT - выдача младшего байта счетчика команд PC;

● РСН OUT - выдача старшего байта счетчика команд PC;

● DPH - старший байт регистра указателя данных DPTR, который используется в качестве регистра для косвенной адресации в командах MOVX @DPTR,A и MOVX A,@DPTR;

● P2 SFR - защелки порта P2;

● INS IN - ввод байта инструкции (команды) из памяти программ;

● ADDR OUT - выдача младшего байта адреса внешней памяти данных из регистров Rm (m = 0, 1) или из регистра DPL (младшего регистра DPTR). Порты ввода–вывода. Назначение портов. Порты Р0, P1, P2, Р3 предназначены для обмена информацией между МК и внешними устройствами, A также для выполнения следующих функций:

● через порт Р0 выводится младший байт адреса А7…A0; выводится из МК и вводится в МК байт данных при работе с внешней памятью программ и внешней памятью данных (с разделением во времени);

● через порт P2 выводится старший байт адреса A15…А8 при работе с внешней памятью программ и внешней памятью данных (только при использовании команд MOVX A,@DPTR и MOVX @DPTR,A);

● линии порта Р3 могут быть задействованы на выполнение альтернативных функций, если в фиксатор–защелку этой линии занесена 1, в противном случае на выводе линии фиксируется 0. Альтернативные функции выводов порта P3 приведены в табл. 7.1.3.

Схемные особенности портов

На рис. 7.1.13 показаны схемы для одного канала каждого из портов МК, включающего в себя:

● защелку для фиксации принимаемого бита данных;

● выходной усилительный каскад (драйвер);

● узел связи с выходным каскадом (за исключением P2);

● цепь для передачи бита данных со стороны вывода порта, состоящую из буферов В2 и В3 (для порта Р4). Защелкой служит D–триггер, тактируемый внутренним сигналом «Запись в защелку». Бит данных с прямого выхода D–триггера может быть считан программно через буфер В1 сигналом «Чтение защелки» на линию внутренней шины данных (ШД) МК.

Выходной каскад порта Р0 представляет собой инвертор, особенности которого проявляются в том, что нагрузочный транзистор VT2 открывается только при обращениях к внешней памяти (при передаче через порт адреса и данных). Во всех других режимах нагрузочный транзистор закрыт. Поэтому для использования Р0 (рис. 7.1.13, а) в качестве выходного порта общего назначения к его выводам необходимо подключить внешние нагрузочные резисторы. При записи 1 в защелку порта инверторный транзистор VT1 запирается и внешний вывод порта Р0.Х переводится в высокоомное состояние. В этом режиме вывод порта Р0.Х может служить входом. Если порт Р0 используется как порт ввода/вывода общего назначения, каждый из его выводов Р0.Х может независимо от других работать как вход или как выход. Выходные каскады портов P1, P2, Р3 (рис. 7.1.13, б, в, г) выполнены по схемам инверторов с внутренним нагрузочным резистором, в качестве которого использован транзистор VT2.

Для уменьшения времени переключения при переходе выводов портов из состояния 0 в состояние 1 параллельно нагрузочному транзистору VT2 введен дополнительный транзистор VT3. Транзистор VT3 с помощью элементов в цепи затвора отпирается на время, равное двум периодам колебаний задающего кварцевого генератора (в течение фаз S1P1, S2P2 машинного цикла). Выходные каскады портов Р0, P2 (рис. 7.1.13, A, в) с помощью мультиплексора MX могут быть подключены либо к защелкам, либо к внутренним шинам «Адрес/ данные» и «Адрес». Выходной каскад порта P1 (рис. 7.1.13, 6) постоянно подключен к защелке.

Если вывод порта Р3 является выходом и его защелка содержит 1, то его выходным каскадом управляет аппаратно внутренний сигнал «Альтернативная функция выхода», обеспечивающий выполнение соответствующей альтернативной функции, т.е. на внешнем выводе формируется один из сигналов ¯WR,¯RD или RxD. Если же вывод порта задействован на вход, то поступающий на него альтернативный сигнал (TxD, ¯INT0, ¯INT1, Т0, Т1) передается на внутреннюю линию «Альтернативная функция входа».

Режим записи в порт.

При выполнении команды записи в порт новое значение записывается в защелку в фазе S6P2 и выводится непосредственно на выходной контакт порта в фазе S1P1 следующего машинного цикла.

Режим чтения порта

Команды чтения портов считывают информацию непосредственно с внешних контактов выводов порта или с выходов защелок. В первом случае бит данных с вывода порта считывается программно через буфер В2 сигналом «Чтение выводов» на линию внутренней шины данных (ШД) МК. Отметим, что сигналы «Запись в защелку», «Чтение защелки», «Чтение выводов» вырабатываются аппаратно при выполнении соответствующих команд.

Во втором случае реализуется так называемый режим «Чтение-Модификация-Запись», в котором команда считывает сигнал состояния защелки, при необходимости модифицирует его и затем записывает обратно в защелку. Режим «Чтение-Модификация-Запись» реализуется при выполнении следующих команд: ANL, ORL, XRL, JBC; CPL; INC; DEC; DJNC; MOV PX,Y; CLR PX.Y; SETB PX,Y.

Чтение информации с выходов защелок позволяет исключить ошибки при интерпретации логического уровня на выводе порта. Продолжение статьи читайте во .

АРХИТЕКТУРА МИКРОКОНТРОЛЛЕРОВ СЕМЕЙСТВА MCS -51

Конспект лекций по курсам

«Микропроцессоры в системах контроля», «Микропроцессорная техника»

«Микропроцессорные средства и системы»

для студентов всех форм обучения специальностей

072000 – Стандартизация и сертификация

210200 – Автоматизация технологических процессов

230104 – Системы автоматизированного проектирования

Тамбов 2005

ВВЕДЕНИЕ.. 3

1. СТРУКТУРА МИКРОКОНТРОЛЛЕРА INTEL 8051. 3

1.1. Организация памяти. 5

1.2. Арифметико-логическое устройство. 6

1.3. Резидентная память программ и данных. 7

1.4. Аккумулятор и регистры общего назначения. 8

1.5. Регистр слова состояния программы и его флаги. 9

1.6. Регистры-указатели. 10

1.7. Регистры специальных функций. 11

1.8. Устройство управления и синхронизации. 11

1.9. Параллельные порты ввода/вывода информации. 12

1.10. Таймеры/счетчики. 13

1.11. Последовательный порт. 18

1.11.1. Регистр SBUF.. 18

1.11.2. Режимы работы последовательного порта. 18

1.11.3. Регистр SCON.. 19

1.11.4. Скорость приёма/передачи. 21

1.12. Система прерываний. 22

2. СИСТЕМА КОМАНД МИКРОКОНТРОЛЛЕРА INTEL 8051. 26

2.1. Общие сведения. 26

2.1.1. Типы команд. 27

2.1.2. Типы операндов. 28

2.1.3. Способы адресации данных. 30

2.1.4. Флаги результата. 31

2.1.5. Символическая адресация. 32

2.2. Команды передачи данных. 33

2.2.1. Структура информационных связей. 33

2.2.2. Обращение к аккумулятору. 33

2.2.3. Обращение к внешней памяти данных. 34

2.2.4. Обращение к памяти программ.. 34

2.2.5. Обращение к стеку. 35

2.3. Арифметические операции. 35

2.4. Логические операции. 39

2.5. Команды передачи управления. 43

2.5.1. Длинный переход. 43

2.5.2. Абсолютный переход. 43

2.5.3. Относительный переход. 44

2.5.4. Косвенный переход. 44

2.5.5. Условные переходы.. 44

2.5.6. Подпрограммы.. 47

2.6. Операции с битами. 48

Контрольные вопросы... 49

ЛИТЕРАТУРА.. 50

Приложение СИСТЕМА КОМАНД INTEL 8051. 51

ВВЕДЕНИЕ

С 80-х годов 20 века в микропроцессорной технике выделился самостоятельный класс интегральных схем – однокристальные микроконтроллеры, которые предназначены для встраивания в приборы различного назначения. От класса однокристальных микропроцессоров их отличает наличие внутренней памяти, развитые средства взаимодействия с внешними устройствами.

Широкое распространение получили 8-разрядных однокристальные микроконтроллеры семейства MCS-51. Это семейство образовалось на основе микроконтроллера Intel 8051, получившего большую популярность у разработчиков микропроцессорных систем контроля благодаря удачно спроектированной архитектуры. Архитектура микроконтроллера это совокупность внутренних и внешних программно доступных аппаратных ресурсов и системы команд.

В последствии фирма Intel выпустила около 50 моделей на базе операционного ядра микроконтроллера Intel 8051. Одновременно многие другие фирмы, такие как Atmel, Philips начали производство своих микроконтроллеров разработанных в стандарте MCS-51. Существует также и отечественный аналог микроконтроллера Intel 8051 - микросхема К1816ВЕ51.

2. СТРУКТУРА МИКРОКОНТРОЛЛЕРА INTEL 8051

Микроконтроллер Intel 8051 выполнен на основе высокоуровневой n-МОП технологии. Его основные характеристики следующие:

· восьмиразрядный центральный процессор, оптимизированный для реализации функций управления;

· встроенный тактовый генератор (максимальная частота 12 МГц);

· адресное пространство памяти программ - 64 Кбайт;

· адресное пространство памяти данных - 64 Кбайт;

· внутренняя память программ - 4 Кбайт;

· внутренняя память данных - 128 байт;

· дополнительные возможности по выполнению операций булевой алгебры (побитовые операции);

· 2 шестнадцатиразрядных многофункциональных таймера/счетчика;

· полнодуплексный асинхронный приемопередатчик (последовательный порт);

· векторная система прерываний с двумя уровнями приоритета и пятью источниками событий.

Рисунок 1 - Структурная схема микроконтроллера Intel 8051

Основу структурной схемы (рис. 1) образует внутренняя двунаправленная 8-разрядная шина, которая связывает между собой основные узлы и устройства микроконтроллера: резидентную память программ (RPM), резидентную память данных (RDM), арифметико-логическое устройство (ALU), блок регистров специальных функций, устройство управления (CU), параллельные порты ввода/вывода (P0-P3), а также программируемые таймеры и последовательный порт.

2.1. Организация памяти

Данный микроконтроллер имеет встроенную (резидентную) и внешнюю память программ и данных. Резидентная память программ (RPM) имеет объем 4 Кбайт, резидентная память данных (RDM) – 128 Байт.

В зависимости от модификации микроконтроллера RPM выполняется в виде масочного ПЗУ, однократно программируемого либо репрограммируемого ПЗУ.

При необходимости пользователь может расширять память программ установкой внешнего ПЗУ. Доступ к внутреннему или внешнему ПЗУ определяется значением сигнала на выводе ЕА (External Access):

EA=VCC (напряжение питания) - доступ к внутреннему ПЗУ;

EA=VSS (потенциал земли) - доступ к внешнему ПЗУ.

Внешняя память программ и данных может составлять по 64 Кбайт и адресоваться с помощью портов P0 и P2. На рис.2 представлена карта памяти Intel 8051.

|

|

Рисунок 2 - Организация памяти Intel 8051

Рисунок 2 - Организация памяти Intel 8051

Строб чтения внешнего ПЗУ - (Program Store Enable) генерируется при обращении к внешней памяти программ и является неактивным во время обращения к ПЗУ, расположенному на кристалле.

Область нижних адресов памяти программ (рис. 3) используется системой прерываний. Архитектура микросхемы INTEL 8051 обеспечивает поддержку пяти источников прерываний. Адреса, по которым передается управление по прерыванию, называются векторами прерывания.

Рисунок 3 - Карта нижней области программной памяти

2.2. Арифметико-логическое устройство

8-битное арифметико-логическое устройство (ALU) может выполнять арифметические операции сложения, вычитания, умножения и деления; логические операции И, ИЛИ, исключающее ИЛИ, а также операции циклического сдвига, сброса, инвертирования и т. п. К входам подключены программно-недоступные регистры T1 и T2, предназначенные для временного хранения операндов, схема десятичной коррекции (DCU) и схема формирования признаков результата операции (PSW).

Простейшая операция сложения используется в ALU для инкрементирования содержимого регистров, продвижения регистра-указателя данных (RAR) и автоматического вычисления следующего адреса резидентной памяти программ. Простейшая операция вычитания используется в ALU для декрементирования регистров и сравнения переменных.

Простейшие операции автоматически образуют “тандемы” для выполнения таких операций, как, например, инкрементирование 16-битных регистровых пар. В ALU реализуется механизм каскадного выполнения простейших операций для реализации сложных команд. Так, например, при выполнении одной из команд условной передачи управления по результату сравнения в ALU трижды инкрементируется счётчик команд (PC), дважды производится чтение из RDM, выполняется арифметическое сравнение двух переменных, формируется 16-битный адрес перехода и принимается решение о том, делать или не делать переход по программе. Все перечисленные операции выполняются всего лишь за 2 мкс.

Важной особенностью ALU является его способность оперировать не только байтами, но и битами. Отдельные программно-доступные биты могут быть установлены, сброшены, инвертированы, переданы, проверены и использованы в логических операциях. Эта способность достаточно важна, поскольку для управления объектами часто применяются алгоритмы, содержащие операции над входными и выходными булевыми переменными, реализация которых средствами обычных микропроцессоров сопряжена с определенными трудностями.

Таким образом, ALU может оперировать четырьмя типами информационных объектов: булевыми (1 бит), цифровыми (4 бита), байтными (8 бит) и адресными (16 бит). В ALU выполняется 51 различная операция пересылки или преобразования этих данных. Так как используется 11 режимов адресации (7 для данных и 4 для адресов), то путем комбинирования операции и режима адресации базовое число команд 111 расширяется до 255 из 256 возможных при однобайтном коде операции.

2.3. Резидентная память программ и данных

Резидентные (размещённые на кристалле) память программ (RPM) и память данных (RDM) физически и логически разделены, имеют различные механизмы адресации, работают под управлением различных сигналов и выполняют разные функции.

Память программ RPM имеет емкость 4 Кбайта и предназначена для хранения команд, констант, управляющих слов инициализации, таблиц перекодировки входных и выходных переменных и т. п. Память имеет 16-битную шину адреса, через которую обеспечивается доступ из программного счётчика PC или из регистра-указателя данных (DPTR). DPTR выполняет функции базового регистра при косвенных переходах по программе или используется в операциях с таблицами.

Память данных RDM предназначена для хранения переменных в процессе выполнения прикладной программы, адресуется одним байтом и имеет емкость

128 байт. Кроме того, к её адресному пространству примыкают адреса регистров специальных функций, которые перечислены в табл. 1.

Память программ, так же как и память данных, может быть расширена до

64 Кбайт путем подключения внешних микросхем.

Таблица 1

Блок регистров специальных функций

|

Наименование | ||||

|

Аккумулятор | ||||

|

Регистр-расширитель аккумулятора | ||||

|

Слово состояния программы | ||||

|

Регистр-указатель стека | ||||

|

Регистр-указатель данных | ||||

|

Регистр приоритетов прерываний | ||||

|

Регистр маски прерываний | ||||

|

Регистр режима таймера/счётчика | ||||

|

Регистр управления/статуса таймера | ||||

|

Таймер 0 (старший байт) | ||||

|

Таймер 0 (младший байт) | ||||

|

Таймер 1 (старший байт) | ||||

|

Таймер 1 (младший байт) | ||||

|

Регистр управления приёмопередатчиком | ||||

|

Буфер приёмопередатчика | ||||

|

Регистр управления мощностью |

Примечание. Регистры, имена которых отмечены знаком (*), допускают адресацию отдельных битов.

2.4. Аккумулятор и регистры общего назначения

Аккумулятор (A) является источником операнда и местом фиксации результата при выполнении арифметических, логических операций и ряда операций передачи данных. Кроме того, только с использованием аккумулятора могут быть выполнены операции сдвигов, проверка на нуль, формирование флага паритета и т. п.

В распоряжении пользователя имеется четыре банка по 8 регистров общего назначения R0–R7 (рис. 9). Однако возможно использование регистров только одного из четырёх банков, который выбирается с помощью бит регистра PSW.

2.5. Регистр слова состояния программы и его флаги

При выполнении многих команд в ALU формируется ряд признаков операции (флагов), которые фиксируются в регистре слова состояния программы (PSW). В табл. 2 приводится перечень флагов PSW, даются их символические имена и описываются условия их формирования.

Таблица 2

Формат слова состояния программы PSW

|

Имя и назначение |

||

|

Флаг переноса. Устанавливается и сбрасывается аппаратно или программно при выполнении арифметических и логических операций |

||

|

Флаг вспомогательного переноса. Устанавливается и сбрасывается только аппаратно при выполнении команд сложения и вычитания и сигнализирует о переносе или займе в бите 3 |

||

|

Флаг 0. Может быть установлен, сброшен или проверен программой как флаг, специфицируемый пользователем |

||

|

Выбор банка регистров. Устанавливается и сбрасывается программно для выбора рабочего банка регистров (табл. 3) |

||

|

Флаг переполнения. Устанавливается и сбрасывается аппаратно при выполнении арифметических операций |

||

|

Не используется |

||

|

Флаг паритета. Устанавливается и сбрасывается аппаратно в каждом цикле и фиксирует нечётное/чётное число единичных битов в аккумуляторе, т. е. выполняет контроль по четности |

Таблица 3

Выбор рабочего банка регистров

|

Границы адресов |

|||

Наиболее “активным” флагом PSW является флаг переноса, который принимает участие и модифицируется в процессе выполнения множества операций, включая сложение, вычитание и сдвиги. Кроме того, флаг переноса (CY) выполняет функции “булева аккумулятора” в командах, манипулирующих с битами. Флаг переполнения (OV) фиксирует арифметическое переполнение при операциях над целыми числами со знаком и делает возможным использование арифметики в дополнительных кодах. ALU не управляет флагами селекции банка регистров (RS0, RS1), их значение полностью определяется прикладной программой и используется для выбора одного из четырёх регистровых банков.

В виде байта регистр PSW может быть представлен следующим образом:

В микропроцессорах, архитектура которых опирается на аккумулятор, большинство команд работают с ним, используя неявную адресацию. В Intel 8051 дело обстоит иначе. Хотя процессор имеет в своей основе аккумулятор, он может выполнять множество команд и без его участия. Например, данные могут быть переданы из любой ячейки RDM в любой регистр, любой регистр может быть загружен непосредственным операндом и т. д. Многие логические операции могут быть выполнены без участия аккумулятора. Кроме того, переменные могут быть инкрементированы, декрементированы и проверены без использования аккумулятора. Флаги и управляющие биты могут быть проверены и изменены аналогично.

2.6. Регистры-указатели

8-битный указатель стека (SP) может адресовать любую область RDM. Его содержимое инкрементируется прежде, чем данные будут запомнены в стеке в ходе выполнения команд PUSH и CALL. Содержимое SP декрементируется после выполнения команд POP и RET. Подобный способ адресации элементов стека называют прединкрементным/постдекрементным. В процессе инициализации микроконтроллера после сигнала RST в SP автоматически загружается код 07Н. Это значит, что если прикладная программа не переопределяет стек, то первый элемент данных в стеке будет располагаться в ячейке RDM с адресом 08Н.

Двухбайтный регистр-указатель данных DPTR обычно используется для фиксации 16-битного адреса в операциях с обращением к внешней памяти. Командами микроконтроллера регистр-указатель данных может быть использован или как 16-битный регистр, или как два независимых 8-битных регистра (DPH и DPL).

2.7. Регистры специальных функций

Регистры с символическими именами IP, IE, TMOD, TCON, SCON и PCON используются для фиксации и программного изменения управляющих бит и бит состояния схемы прерывания, таймера/счётчика, приёмопередатчика последовательного порта и для управления энергопотреблением. Подробно их организация будет описана в разделах 1.8-1.12, при рассмотрении особенностей работы микроконтроллера в различных режимах.

2.8. Устройство управления и синхронизации

Кварцевый резонатор, подключаемый к внешним выводам микроконтроллера, управляет работой внутреннего генератора, который в свою очередь формирует сигналы синхронизации. Устройство управления (CU) на основе сигналов синхронизации формирует машинный цикл фиксированной длительности, равной 12 периодам генератора. Большинство команд микроконтроллера выполняется за один машинный цикл. Некоторые команды, оперирующие с 2-байтными словами или связанные с обращением к внешней памяти, выполняются за два машинных цикла. Только команды деления и умножения требуют четырех машинных циклов. На основе этих особенностей работы устройства управления производится расчёт времени исполнения прикладных программ.

На схеме микроконтроллера к устройству управления примыкает регистр команд (IR). В его функцию входит хранение кода выполняемой команды.

Входные и выходные сигналы устройства управления и синхронизации:

1. PSEN – разрешение программной памяти,

2. ALE – выходной сигнал разрешения фиксации адреса,

3. PROG – сигнал программирования,

4. EA – блокировка работы с внутренней памятью,

5. VPP – напряжение программирования,

6. RST – сигнал общего сброса,

7. VPD – вывод резервного питания памяти от внешнего источника,

8. XTAL – входы подключения кварцевого резонатора.

2.9. Параллельные порты ввода/вывода информации

Все четыре порта (P0-P3) предназначены для ввода или вывода информации побайтно. Каждый порт содержит управляемые регистр-защёлку, входной буфер и выходной драйвер.

Выходные драйверы портов P0 и P2, а также входной буфер порта P0 используются при обращении к внешней памяти. При этом через порт P0 в режиме временного мультиплексирования сначала выводится младший байт адреса, а затем выдается или принимается байт данных. Через порт P2 выводится старший байт адреса в тех случаях, когда разрядность адреса равна 16 бит.

Все выводы порта P3 могут быть использованы для реализации альтернативных функций, перечисленных в табл. 4. Эти функции могут быть задействованы путем записи 1 в соответствующие биты регистра-защёлки (P3.0-P3.7) порта P3.

Таблица 4

Альтернативные функции порта P3

|

Имя и назначение |

||

|

Чтение. Активный сигнал низкого уровня формируется аппаратно при обращении к внешней памяти данных |

||

|

Запись. Активный сигнал низкого уровня формируется аппаратно при обращении к внешней памяти данных |

||

|

Вход таймера/счётчика 1 или тест-вход |

||

|

Вход таймера/счётчика 0 или тест-вход |

||

|

Вход запроса прерывания 1. Воспринимается сигнал низкого уровня или срез |

||

|

Вход запроса прерывания 0. Воспринимается сигнал низкого уровня или срез |

||

|

Выход передатчика последовательного порта в режиме UART. Выход синхронизации в режиме регистра сдвига |

||

|

Вход приёмника последовательного порта в режиме UART. Ввод/вывод данных в режиме регистра сдвига |

Порт 0 является двунаправленным, а порты 1-3 - квазидвунаправленными. Каждая линия портов может быть использована независимо для ввода или вывода.

По сигналу RST в регистры-защёлки всех портов автоматически записываются единицы, настраивающие их тем самым на режим ввода.

Все порты могут быть использованы для организации ввода/вывода информации по двунаправленным линиям передачи. Однако порты P0 и P2 не могут быть использованы для этой цели в случае, если система имеет внешнюю память, связь с которой организуется через общую разделяемую шину адреса/данных, работающую в режиме временного мультиплексирования.

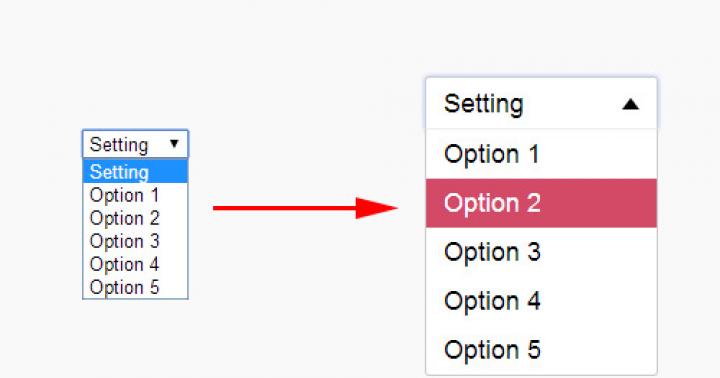

Обращение к портам ввода/вывода возможно с использованием команд, оперирующих с байтом, отдельным битом, произвольной комбинацией битов. При этом в тех случаях, когда порт является одновременно операндом и местом назначения результата, устройство управления автоматически реализует специальный режим, который называется “чтение-модификация-запись”. Этот режим обращения предполагает ввод сигналов не с внешних выводов порта, а из его регистра-защёлки, что позволяет исключить неправильное считывание ранее выведенной информации. Этот механизм обращения к портам реализован в командах:

УДК 681.5, 681.325.5 (075.8)

ББК 32.973.202-018.2 я 73

Щербина А. Н. Вычислительные машины, системы и сети. Микроконтроллеры и микропроцессоры в системах управления: у чеб. пособие / А.Н. Щербина, П.А. Нечаев- СПб.: Из-во Политехн. ун-та, 2012.-226 с.

Соответствует содержанию государственного образовательного стандарта направлений подготовки и специальностей в области управления в технических системах, электроэнергетики и электротехники и содержанию примерной учебной программы дисциплины «Вычислительные машины, системы и сети».

Рассмотрены фундаментальные вопросы логической организации микропроцессорных систем на примере базовой архитектуры микроконтроллерного семейства MCS-51 фирмы Intel. Описана технология программирования микроконтроллеров на языках Ассемблер и СИ.

Может быть полезным для студентов и преподавателей высших технических заведений, специалистов по автоматизации технологических процессов и производственного оборудования, а также для инженеров-проектировщиков микропроцессорных систем.

Также соответствует содержанию государственного образовательного стандарта дисциплин «Микроконтроллеры и микропроцессоры в системах управления» и «Электронные устройства автоматики» бакалаврской, инженерной и магистерской подготовки по направлению 140400 «Электроэнергетика и электротехника».

Печатается по решению редакционно-издательского совета

Санкт-Петербургского государственного политехнического университета.

© Щербина А. Н., Нечаев П. А., 2012

© Санкт-Петербургский государственный

политехнический университет, 2012

ISBN 978-5-7422-3553-8

Введение.. 7

Глава 1. Архитектура семейства MCS51. 10

1.1 Общие характеристики 10

1.2 Структурная схема 11

1.3 Назначение выводов микроконтроллера 8051 15

1.4 Организация памяти 17

1.4.1 Память программ (ПЗУ) 18

1.4.2 Память данных (ОЗУ) 19

1.4.3 Регистры специальных функций. 20

1.4.4 Регистр флагов (PSW) 23

1.5 Устройство управления и синхронизации 26

1.6 Организация портов ввода-вывода 27

1.6.1 Общие сведения. 27

1.6.2 Альтернативные функции. 27

1.7. Таймеры / счетчики микроконтроллеров семейства 8051. 28

1.7.1. Структура таймеров-счетчиков. 28

1.7.2 Режимы работы таймеров-счетчиков. 30

1.8. Последовательный порт 32

1.8.1. Структура последовательного порта. 32

1.8.2. Регистр управления/статуса приемопередатчика SCON.. 34

1.8.3. Регистр управления мощностью PCON.. 36

1.9. Система прерываний 37

1.9.1. Структура системы прерываний. 37

1.9.2 Выполнение подпрограммы прерывания. 40

Глава 2. Особенности микроконтроллера 80C51GB.. 42

2.1 Функциональные особенности 42

2.2 Порты I/O P0-P5 43

2.2.1 Функционирование портов ввода-вывода. 43

2.2.2 Запись в порт.. 46

2.3 Особенности системы прерываний 8XC51GB.. 49

Разрешение/запрещение прерываний. 50

Управление приоритетами прерываний. 51

Внешние прерывания. 54

2.3. Узел АЦП 56

2.4. Аппаратный сторожевой таймер 61

2.5. Обнаружение сбоя тактового генератора 63

2.6. Матрица программируемых счётчиков РСА 64

2.6.1. Структура PCA.. 64

2.6.2. Регистр режима счётчика РСА (CMOD) 66

2.6.3. Регистр управления счётчика РСА (CON) 67

2.6.4. Модули сравнения/фиксации. 68

2.7. Расширенный последовательный порт 76

2.8. Таймеры/счетчики 79

Расположение выводов микроконтроллеров группы 8XC51GB.. 86

Глава 3. Программирование MK 8051GB.. 89

3.1. Программная модель 89

3.2 Типы данных 93

3.3 Способы адресации данных 93

3.4 Система команд 95

3.4.1 Общая характеристика. 95

3.4.2 Типы команд. 96

3.4.3 Типы операндов. 97

3.4.4 Команды пересылки данных микроконтроллера. 98

3.4.5 Команды арифметических операций 8051. 101

3.4.6 Команды логических операций микроконтроллера 8051. 104

3.4.7 Команды операций над битами микроконтроллера 8051. 106

3.5 Отладка программ 111

Глава 4. Язык программирования ASM-51. 112

4.2 Запись текста программы 113

4.3 Алфавит языка. 114

4.4 Идентификаторы. 115

4.5 Числа 117

4.6 Директивы 118

4.7 Реализация подпрограмм на языке ASM51 122

4.7.1 Структура подпрограммы-процедуры на языке ASM51. 122

4.7.2 Передача переменных-параметров в подпрограмму. 123

4.7.3 Реализация подпрограмм-функций на языке ASM51. 123

4.7.4 Реализация подпрограмм обработки прерываний на языке ASM51. 124

4.8 Структурное программирование на языке ассемблера. 125

4.9 Особенности трансляции многомодульных программ.. 126

4.10 Использование сегментов 128

4.10.1 Разбиение памяти МК на сегменты.. 128

4.10.2 Абсолютные сегменты памяти. 129

4.10.2 Перемещаемые сегменты памяти. 131

Глава 5. Язык программирования С-51. 134

5.1 Общая характеристика языка 134

5.3 Структура программ С-51 136

5.3. Элементы языка программирования С-51 138

5.3.1. Символы.. 138

5.3.2. Лексические единицы, разделители и использование пробелов. 141

5.3.3 Идентификаторы.. 142

5.3.4 Ключевые слова. 143

5.3.5 Константы.. 143

5.4. Выражения в операторах языка 146

программирования C-51 146

5.5. Приоритеты выполнения операций 148

5.6. Операторы языка программирования C-51 149

5.6.1. Операторы объявления. 150

5.6.2 Исполняемые операторы.. 150

5.6.3 Оператор присваивания. 151

5.6.4 Условный оператор. 151

5.6.5 Структурный оператор {}. 152

5.6.6 Оператор цикла for. 152

5.6.7 Оператор цикла с проверкой условия до тела цикла while. 153

5.6.8 Оператор цикла с проверкой условия после тела цикла do while. 154

5.6.9 Оператор break. 155

5.6.10 Оператор continue. 155

5.6.11 Оператор выбора switch. 155

5.6.12 Оператор безусловного перехода goto. 157

5.6.13 Оператор выражение. 158

5.6.14 Оператор возврата из подпрограммы return. 158

5.6.15 Пустой оператор. 158

5.7. Объявление переменных в языке программирования C-51. 159

5.7.1. Объявление переменной. 159

5.7.3 Целые типы данных. 161

5.7.4 Числа с плавающей запятой. 162

5.7.5 Переменные перечислимого типа. 162

5.7.6. Объявление массивов в языке программирования C-51. 164

5.7.7. Структуры.. 165

5.7.8. Объединения (смеси) 166

5.8. Использование указателей в языке C-51 167

5.8.1. Объявление указателей. 167

5.8.2. Нетипизированные указатели. 168

5.8.3. Память зависимые указатели. 169

5.9. Объявление новых типов переменных 169

5.10. Инициализация данных 170

5.11. Использование подпрограмм в языке программирования С-51. 170

5.11.1. Определение подпрограмм.. 171

5.11.2. Параметры подпрограмм.. 173

5.11.3. Предварительное объявление подпрограмм.. 174

5.11.4 Вызов подпрограмм.. 176

5.11.5 Рекурсивный вызов подпрограмм.. 176

5.11.6 Подпрограммы обработки прерываний. 177

5.11.7 Области действия переменных и подпрограмм.. 178

5.12. Многомодульные программы 179

Глава 6. Подготовка программ в интегрированной среде разработки Keil μVision2. 182

6.1 Создание проекта на языке ASM-51 182

6.2 Пример создания проекта на языке C для учебного контроллера в интегрированной среде разработки Keil μVision2 188

Глава 7. Описание учебного контроллера.. 199

7.1. Структура контроллера 199

7.2. Адресное пространство 200

7.2.1. Распределение памяти. 200

7.2.2 Внешняя память. 201

7.2.3. Внутренняя память данных. 202

7.3. Распределение портов ввода-вывода 202

7.4. Последовательный порт………………………………...203

7.5. Работа с ЖКИ 205

7.6. Панели контроллера…………………………………………………213

ПРИЛОЖЕНИЕ П2 СТРУКТУРА ОТЧЁТА О ЛАБРОРАТОРНОЙ РАБОТЕ……..217

Приложение П3 Коды машинных команд. 217

Список литературы... 224

Введение

В освоении специальностей, связанных с автоматизацией технологических процессов и производств, изучение микроконтроллеров является одним из важных разделов.

В мире происходит непрерывное развитие и появление все новых и новых 16- и 32-разрядных микроконтроллеров и микропроцессоров, но наибольшая доля мирового микропроцессорного рынка и по сей день остается за 8-разрядными устройствами. По всем прогнозам аналитических компаний на ближайшее время, лидирующее положение 8-разрядных микроконтроллеров на мировом рынке сохранится.

В настоящее время среди всех 8-разрядных микроконтроллеров семейство MCS-51 является несомненным лидером по количеству разновидностей и количеству компаний, выпускающих его модификации. Оно получило свое название от первого представителя этого семейства - микроконтроллера 8051. Удачный набор периферийных устройств, возможность гибкого выбора внешней или внутренней программной памяти и приемлемая цена обеспечили этому микроконтроллеру успех на рынке.

Достоинства семейства MCS-51:

· архитектура, являющаяся стандартом де-факто;

· чрезвычайная широта семейства и разнообразие возможностей;

· наличие высокопроизводительных и расширенных версий процессоров;

· значительное число свободно доступных программных и аппаратурных наработок;

· легкость аппаратного программирования, в т. ч. и внутрисхемного;

· дешевизна и доступность базовых чипов;

· наличие специализированных версий контроллеров для особых условий применения

· наличие версий контроллеров с пониженным уровнем электромагнитных помех;

· широкая известность среди разработчиков старшего поколения, как в мире, так и в странах СНГ;

· поддержка архитектуры ведущими учебными заведениями мира.

И, наконец, главное преимущество: освоив базовый чип семейства, легко начнеть работать с такими вычислительными «монстрами», как микроконтроллеры Cygnal, Dallas Semiconductor, Analog Devices, Texas Instruments.

В состав семейства MCS-51 входит целый ряд микросхем от самых простых микроконтроллеров до достаточно сложных. На сегодняшний день существует более 200 модификаций микроконтроллеров семейства 8051, выпускаемых почти 20-ю компаниями. Каждый год появляются все новые варианты представителей этого семейства.

Основными направлениями развития являются:

· увеличение быстродействия (повышение тактовой частоты и переработка архитектуры);

· снижение напряжения питания и энергопотребления;

· увеличение объема ОЗУ и FLASH памяти на кристалле с возможностью внутрисхемного программирования;

· введение в состав периферии микроконтроллера сложных устройств типа системы управления приводами, CAN и USB интерфейсов и т.п.

Микроконтроллеры семейства MCS-51 позволяют выполнять как задачи управления различными устройствами, так и реализовывать отдельные узлы аналоговой схемы. Все микросхемы этого семейства работают с одной и той же системой команд. Большинство из них выполняется в одинаковых корпусах с совпадающей цоколевкой (нумерация ножек для корпуса). Это позволяет использовать для разработанного устройства микросхемы разных фирм - производителей без переделки принципиальной схемы устройства и программы.

Основными производителями разновидностей 51-го семейства в мире являются фирмы Philips, Siemens, Intel, Atmel, Dallas, Temic, Oki, AMD, MHS, Gold Star, Winbond, Silicon Systems и ряд других.

Характеристики аналогов микроконтроллеров семейства MCS-51 (Intel 8XC51FA, 8XC51GB, 80С152) с расширенными возможностями приведены в табл. В.1.

Таблица В.1

| ОЗУ | ПЗУ | РСА | АЦП | WDT | T/C | Послед. Каналы | Особенности | |

| Atmel: AT89C2051 | ||||||||

| - | - | - | - | UART | Flash 2 Кб | |||

| AT89C4051 | - | - | - | - | UART | Flash 4 Кб | ||

| AT89S4D12 | 128K | - | - | - | UART, SPI | Flash 4 Кб | ||

| DALLAS Semiconductor: DS5000FP | ||||||||

| - | - | - | + | UART | Bootstrap loader | |||

| DS5001FP | - | - | - | + | UART | Bootstrap loader | ||

| DS8xC520 | 16K | - | - | + | 2xUART | 2 DPTR | ||

| SIEMENS: C505C | ||||||||

| 16K | - | + | + | UART, CAN | 8 DPTR | |||

| C515C | 64K | - | + | + | UART+ SSC+CAN | 4 ШИМ, 8 DPTR | ||

| Philips: *89C51RA+ | ||||||||

| - | + | - | + | UART | 2 DPTR, 4 ур. прер., clock out, Flash 8K | |||

| P51XAG1x | 8K | - | - | + | 2 UART | |||

| Intel: 8xC51RA | ||||||||

| 8K | - | + | + | UART | 4 уровня IRQ, clock out | |||

| 8XC196KC | 64K | 16K | - | + | - | UART | 3 ШИМ | |

| 80C196KB | 64K | 8K | - | + | - | UART | ШИМ |

Глава 1. Архитектура семейства MCS51

8-разрядные однокристальные микроконтроллеры семейства MCS-51 приобрели большую популярность у разработчиков микропроцессорных систем контроля благодаря удачно спроектированной архитектуре. Архитектура микроконтроллера – это совокупность внутренних и внешних программно-доступных аппаратных ресурсов и системы команд. Архитектура семейства MCS-51 в значительной мере предопределяется ее назначением - построение компактных и дешевых цифровых устройств. Микроконтроллеры, выполняющие все функции микроЭВМ с помощью единственной микросхемы, получили название однокристальных ЭВМ (ОЭВМ).

Фирма Intel выпустила около 50 моделей на базе операционного ядра микроконтроллера Intel 8051. Одновременно многие другие фирмы, такие как Atmel, Philips, начали производство своих микроконтроллеров, разработанных в стандарте MCS-51.

Общие характеристики

Основные характеристики семейства:

· 8-разрядный центральный процессор (ЦП), ориентированный на управление исполнительными устройствами;

· ЦП имеет встроенную схему 8-разрядного аппаратного умножения и деления чисел;

· наличие в наборе команд большого количества операций для работы с прямоадресуемыми битами даёт возможность говорить о процессоре для работы с битовыми данными (булевом процессоре);

· внутренняя (расположенная на кристалле) память программ масочного или репрограммируемого типа, имеющая для различных кристаллов объём от 4 до 32 Кб, в некоторых версиях она отсутствует;

· не менее чем 128 байтное резидентное ОЗУ данных, которое используется для организации, регистровых банков, стека и хранения пользовательских данных;

· не менее 32-х двунаправленных интерфейсных линий (портов), индивидуально настраиваемых на ввод или вывод информации;

· два 16-битных многорежимных счетчика/таймера, используемых для подсчёта внешних событий, организации временных задержек и тактирования коммуникационного порта;

· двунаправленный дуплексный асинхронный приемопередатчик (UART), предназначенный для организации каналов связи между микроконтроллером и внешними устройствами с широким диапазоном скоростей передачи информации. Имеются средства для аппаратно-программного объединения микроконтроллеров в связанную систему;

· двухуровневая приоритетная система прерываний, поддерживающая не менее 5 векторов прерываний от 4-х внутренних и 2-х внешних источников событий;

· встроенный тактовый генератор.

Структурная схема

Структурная схема контроллера представлена на рис.1.1 и состоит из следующих основных функциональных узлов: блока управления, арифметико-логического устройства, блока таймеров/счетчиков, блока последовательного интерфейса и прерываний, программного счетчика, памяти данных и памяти программ. Двусторонний обмен осуществляется с помощью внутренней 8-разрядной магистрали данных. По такой схеме построены практически все представители семейства MCS-51. Различные микросхемы этого семейства различаются только регистрами специального назначения (в том числе и количеством портов).

Блок управления и синхронизации (Timing and Control) - предназначен для выработки синхронизирующих и управляющих сигналов, обеспечивающих координацию совместной работы блоков ОЭВМ во всех допустимых режимах ее работы. В состав блока управления входят:

устройство формирования временных интервалов;

логика ввода-вывода;

регистр команд;

регистр управления потреблением электроэнергии;

дешифратор команд, логика управления ЭВМ.

Рис. 1.1. Структурная схема контроллера I8051.

Устройство формирования временных интервалов предназначено для формирования и выдачи внутренних синхросигналов фаз, тактов и циклов. Количество машинных циклов определяет продолжительность выполнения команд. Практически все команды ОЭВМ выполняются за один или два машинных цикла, кроме команд умножения и деления, продолжительность выполнения которых составляет четыре машинных цикла. Обозначим частоту задающего генератора через F г. Длительность машинного цикла равна 12/F г или составляет 12 периодов сигнала задающего генератора. Логика ввода - вывода предназначена для приема и выдачи сигналов, обеспечивающих обмен информации с внешними устройствами через порты ввода вывода Р0-Р3.

Регистр команд предназначен для записи и хранения 8-ми разрядного кода операции выполняемой команды. Код операции, с помощью дешифратора команд и логики управления ЭВМ, преобразуется в микропрограмму выполнения команды.

Регистр управления потреблением (PCON) позволяет останавливать работу микроконтроллера для уменьшения потребления электроэнергии и уменьшения уровня помех от микроконтроллера. Еще большего уменьшения потребления электроэнергии и уменьшения помех можно добиться, остановив задающий генератор микроконтроллера. Этого можно достичь при помощи переключения бит регистра управления потреблением PCON. Для варианта изготовления по технологии n-МОП (серия 1816 или иностранных микросхем, в названии которых в середине отсутствует буква "c") регистр управления потреблением PCON содержит только один бит, управляющий скоростью передачи последовательного порта SMOD, а биты управления потреблением электроэнергией отсутствуют.

Арифметико-логическое устройство (ALU) представляет собой параллельное восьмиразрядное устройство, обеспечивающее выполнение арифметических и логических операций. АЛУ состоит из:

регистров аккумулятора, регистров временного хранения TMP1 и TMP2;

ПЗУ констант;

сумматора;

дополнительного регистра (регистра В);

аккумулятора (ACC);

регистра состояния программ (PSW).

Регистр аккумулятор и регистры временного хранения - восьмиразрядные регистры, предназначенные для приема и хранения операндов на время выполнения операций над ними. Эти регистры программно не доступны.

ПЗУ констант обеспечивает выработку корректирующего кода при двоично-десятичном представлении данных, кода маски при битовых операциях и кода констант.

Параллельный восьмиразрядный сумматор представляет собой схему комбинационного типа с последовательным переносом, предназначенную для выполнения арифметических операций сложения, вычитания и логических операций сложения, умножения, неравнозначности и тождественности.

Регистр B - восьмиразрядный регистр, используемый во время операций умножения и деления. Для других инструкций он может рассматриваться как дополнительный сверхоперативный регистр.

Аккумулятор - восьмиразрядный регистр, предназначенный для приема и хранения результата, полученного при выполнении арифметико-логических операций или операций сдвига

Блок последовательного интерфейса и прерываний (ПИП) предназначен для организации ввода - вывода последовательных потоков информации и организации системы прерывания программ. В состав блока входят:

буфер ПИП;

логика управления;

регистр управления;

буфер передатчика;

буфер приемника;

приемопередатчик последовательного порта;

регистр приоритетов прерываний;

регистр разрешения прерываний;

логика обработки флагов прерываний и схема выработки вектора.

Счетчик команд (Program Counter) предназначен для формирования текущего 16-разрядного адреса внутренней памяти программ и 8/16-разрядного адреса внешней памяти программ. В состав счетчика команд входят 16-разрядные буфер РС, регистр РС и схема инкремента (увеличения содержимого на 1).

Память данных (RAM) предназначена для временного хранения информации, используемой в процессе выполнения программы.

Порты P0, P1, P2, P3 являются квазидвунаправленными портами ввода - вывода и предназначены для обеспечения обмена информацией ОЭВМ с внешними устройствами, образуя 32 линии ввода- вывода.

Регистр состояния программы (PSW) предназначен для хранения информации о состоянии АЛУ при выполнении программы.

Память программ (EPROM) предназначена для хранения программ и представляет собой постоянное запоминающее устройство (ПЗУ). В разных микросхемах применяются масочные, стираемые ультрафиолетовым излучением или FLASH ПЗУ.

Регистр указателя данных (DPTR) предназначен для хранения 16 - разрядного адреса внешней памяти данных.

Указатель стека (SP) представляет собой восьмиразрядный регистр, предназначенный для организации особой области памяти данных (стека), в которой можно временно сохранить любую ячейку памяти.

1.3 Назначение выводов микроконтроллера 8051 (рис. 1.2)

· U ss - потенциал общего провода ("земли");

· U cc - основное напряжение питания +5 В;

· X1,X2 - выводы для подключения кварцевого резонатора;

· RST - вход общего сброса микроконтроллера;

· PSEN - разрешение внешней памяти программ, выдается только при обращении к внешнему ПЗУ;

· ALE - строб адреса внешней памяти;

· ЕА - отключение внутренней программной память; уровень 0 на этом входе заставляет микроконтроллер выполнять программу только из внешнего ПЗУ; игнорируя внутреннее(если последнее имеется);

Рис. 1.2. Назначение выводов 8051.

· P1 - восьмибитный квазидвунаправленный порт ввода/вывода, каждый разряд порта может быть запрограммирован как на ввод, так и на вывод информации, независимо от состояния других разрядов;

· P2 - восьмибитный квазидвунаправленный порт, аналогичный Р1, выводы этого порта используются для выдачи адресной информации при обращении к внешней памяти программ или данных (если используется 16-битовая адресация последней). Кроме того, выводы порта используются при программировании для ввода в микроконтроллер старших разрядов адреса;

· РЗ - восьмибитный квазидвунаправленный порт, аналогичный Р1, выводы этого порта могут выполнять ряд альтернативных функций, которые используются при работе таймеров, порта последовательного ввода-вывода, контроллера прерываний, и внешней памяти программ и данных;

· P0 - мультиплексируемый восьмибитный двунаправленный порт ввода-вывода информации, через этот порт в разные моменты времени выводятся младший байт адреса и данные.

Организация памяти

Вся серия MCS-51 имеет гарвардскую архитектуру, то есть раздельные адресные пространства памяти программ и данных. Структура памяти изображена на рис. 1.3.

Объем внутренней (резидентной) памяти программ (ROM, EPROM или OTP ROM), располагаемой на кристалле, в зависимости от типа микросхемы может составлять 0 (ROMless), 4К (базовый кристалл), 8К, 16К или 32К. При необходимости пользователь может расширять память программ установкой внешнего ПЗУ. Доступ к внутреннему или внешнему ПЗУ определяется значением сигнала на выводе ЕА (External Access):

EA=V cc (напряжение питания) - доступ к внутреннему ПЗУ;

EA=V ss (потенциал земли) - доступ к внешнему ПЗУ.

Для кристаллов без ПЗУ(ROMless) вывод ЕА должен быть постоянно подключен к V ss .

|  |

Рис. 1.3. Организация памяти семейства MCS-51

Строб чтения внешнего ПЗУ - (Program Store Enable) генерируется при обращении к внешней памяти программ и является неактивным во время обращения к ПЗУ, расположенному на кристалле. Область нижних адресов памяти программ используется системой прерываний. Архитектура базовой микросхемы 8051обеспечивает поддержку пяти источников прерываний:

· двух внешних прерываний;

· двух прерываний от таймеров;

· прерывания от последовательного порта.

На рис. 1.4 изображена карта нижней области программной памяти.

Рис. 1.4. Карта нижней области программной памяти

Память программ (ПЗУ)

У микроконтроллеров семейства 8051, память программ и память данных являются самостоятельными и независимыми друг от друга устройствами, адресуемыми различными командами и управляющими сигналами.

Объем встроенной памяти программ, расположенной на кристалле микроконтроллера 8051 , равен 4 Кбайт (в семействе до 32). При обращении к внешней памяти программ все микроконтроллеры семейства 8051 всегда используют 16-разрадный адрес, что обеспечивает им доступ к 64 Кбайт ПЗУ. Микроконтроллер обращается к программной памяти при чтении кода операции и операндов (используя счетчик команд PC), а также при выполнении команд копирования байта из памяти программ в аккумулятор. При выполнении команд копирования данных адресация ячейки памяти программ, из которой будут прочитаны данные, может осуществляться с использованием как счетчика PC, так и специального двухбайтового регистра-указателя данных DPTR.

Память данных (ОЗУ)

Объем расположенной на кристалле памяти данных - 128 байт. Объем внешней памяти данных может достигать 64 Кбайт. Первые 32 байта организованы в четыре банка регистров общего назначения, обозначаемых соответственно банк 0 - банк 3. Каждый из них состоит из восьми регистров R0–R7. В любой момент программе доступен, при регистровой адресации, только один банк регистров, номер которого содержится в третьем и четвертом битах слова состояния программы PSW .

Адреса битовой области памяти микроконтроллера 8051

Таблица 1.1

| Адрес байта (Hex) | Адреса битов по разрядам | |||||||

| D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 | |

| 2F | 7F | 7E | 7D | 7C | 7B | 7A | ||

| 2E | ||||||||

| 2D | 6F | 6E | 6D | 6C | 6B | 6A | ||

| 2C | ||||||||

| 2B | 5F | 5E | 5D | 5C | 5B | 5A | ||

| 2A | ||||||||

| 4F | 4E | 4D | 4C | 4B | 4A | |||

| 3F | 3E | 3D | 3C | 3B | 3A | |||

| 2F | 2E | 2D | 2C | 2B | 2A | |||

| 1F | 1E | 1D | 1C | 1B | 1A | |||

| 0F | 0E | 0D | 0C | 0B | 0A | |||

| 20h |

Оставшееся адресное пространство может конфигурироваться разработчиком по своему усмотрению: в нем можно разместить стек, системные и пользовательские области данных. Обращение к ячейкам памяти данных возможно двумя способами. Первый способ - прямая адресация ячейки памяти. В этом случае адрес ячейки является операндом соответствующей команды. Второй способ - косвенная адресация с помощью регистров-указателей R0 или R1: перед выполнением соответствующей команды в один из них должен быть занесен адрес ячейки, к которой необходимо обратиться.

Для обращения к внешней памяти данных используется только косвенная адресация с помощью регистров R0 и R1 или с помощью 16-разрядного регистра-указателя DPTR.

Часть памяти данных представляет собой битовую область, в ней имеется возможность при помощи специальных битовых команд адресоваться к каждому разряду ячеек памяти. Адрес прямо адресуемых битов может быть записан также в виде (АдресБайта).(Разряд). Соответствие этих двух способов адресации можно определить по табл. 1.1.

Архитектура семейства MCS-51 в значительной мере предопределяется ее назначением - построение компактных и дешевых цифровых устройств. Все функции микроЭВМ реализуются с помощью единственной микросхемы. В состав семейства MCS-51 входит целый ряд микросхем от самых простых микроконтроллеров до достаточно сложных. Микроконтроллеры семейства MCS-51 позволяют выполнять как задачи управления различными устройствами, так и реализовывать отдельные узлы аналоговой схемы. Все микросхемы этого семейства работают с одной и той же системой команд , большинство из них выполняется в одинаковых корпусах с совпадающей цоколевкой (нумерация ножек для корпуса). Это позволяет использовать для разработанного устройства микросхемы разных фирм — производителей (таких как Intel, Dallas, Atmel, Philips и т.д.) без переделки принципиальной схемы устройства и программы .

Рисунок 1. Структурная схема контроллера К1830ВЕ751

Структурная схема контроллера представлена на рисунке 1. и состоит из следующих основных функциональных узлов: блока управления, арифметико-логического устройства, блока таймеров/счетчиков, блока последовательного интерфейса и прерываний, программного счетчика, памяти данных и памяти программ. Двусторонний обмен осуществляется с помощью внутренней 8-разрядной магистрали данных. Рассмотрим подробнее назначение каждого блока. По такой схеме построены практически все представители семейства MCS-51 . Различные микросхемы этого семейства различаются только регистрами специального назначения (в том числе и количеством портов). Система команд всех контроллеров семейства MCS-51 содержит 111 базовых команд с форматом 1, 2 или 3 байта и не изменяется при переходе от одной микросхемы к другой. Это обеспечивает прекрасную переносимость программ с одной микросхемы на другую.

Блок управления и синхронизации

Блок управления и синхронизации (Timing and Control) предназначен для выработки синхронизирующих и управляющих сигналов, обеспечивающих координацию совместной работы блоков ОЭВМ во всех допустимых режимах ее работы.В состав блока управления входят:

- устройство формирования временных интервалов,

- логика ввода-вывода,

- регистр команд,

- регистр управления потреблением электроэнергии,

- дешифратор команд, логика управления ЭВМ.

Устройство формирования временных интервалов предназначено для формирования и выдачи внутренних синхросигналов фаз, тактов и циклов. Количество машинных циклов определяет продолжительность выполнения команд. Практически все команды ОЭВМ выполняются за один или два машинных цикла, кроме команд умножения и деления, продолжительность выполнения которых составляет четыре машинных цикла. Обозначим частоту задающего генератора через F г. Тогда длительность машинного цикла равна 12/F г или составляет 12 периодов сигнала задающего генератора. Логика ввода - вывода предназначена для приема и выдачи сигналов, обеспечивающих обмен информации с внешними устройствами через порты ввода вывода Р0-Р3.

Регистр команд предназначен для записи и хранения 8-ми разрядного кода операции выполняемой команды. Код операции, с помощью команд и логики управления ЭВМ, преобразуется в микропрограмму выполнения команды.

Регистр управления потреблением (PCON ) позволяет останавливать работу микроконтроллера для уменьшения потребления электроэнергии и уменьшения уровня помех от микроконтроллера. Еще большего уменьшения потребления электроэнергии и уменьшения помех можно добиться, остановив задающий генератор микроконтроллера. Этого можно достичь при помощи переключения бит регистра управления потреблением PCON. Для варианта изготовления по технологии n-МОП (серия 1816 или иностранных микросхем, в названии которых в середине отсутствует буква "c") регистр управления потреблением PCON содержит только один бит, управляющий скоростью передачи последовательного порта SMOD, а биты управления потреблением электроэнергией отсутствуют.

Вместе со статьей "Архитектура микроконтроллеров MCS-51" читают:

http://сайт/MCS51/tablms.php

http://сайт/MCS51/SysInstr.php

http://сайт/MCS51/port.php

Архитектура микроконтроллеров

Понимание архитектуры микроконтроллеров является ключевым при изучении языков программирования типа ассемблер. Структура ассемблера, формат его команд, адресация операндов и т. д. полностью определяются архитектурой. Целью изучения архитектуры является:

· выявление набора доступных для программирования регистров, их функционального назначения и структуры;

· понимание организации оперативной памяти и порядка ее использования;

· знакомство с типами данных;

· изучение формата машинных команд;

· выяснение организации обработки прерываний.

Архитектура семейства MCS-51 в значительной мере предопределяется ее назначением - построение компактных и дешевых цифровых устройств. Все функции МК реализуются с помощью единственной микросхемы. В состав семейства MCS-51 входит целый ряд микросхем от самых простых микроконтроллеров до достаточно сложных. Микроконтроллеры семейства MCS-51 позволяют выполнять как задачи управления различными устройствами, так и реализовывать отдельные узлы аналоговой схемы. Все микросхемы этого семейства работают с одной и той же системой команд, большинство из них выполняется в одинаковых корпусах с совпадающей цоколевкой (нумерация выводов для корпуса). Это позволяет использовать для разработанного устройства микросхемы разных фирм - производителей (таких какIntel, Dallas, Atmel, Philips и т.д.) без переделки принципиальной схемы устройства и программы.

MCS-51 выполнен по Гарвардской архитектуре, где адресные пространства памяти программ и данных разделены.

Структурная схема контроллера представлена на рис.2.3 и состоит из следующих основных функциональных узлов: блока управления, арифметико-логического устройства, блока таймеров/счетчиков, последовательного интерфейса и прерываний, программного счетчика (счетчика команд), памяти данных и памяти программ.

Двусторонний обмен осуществляется с помощью внутренней 8-разрядной магистрали данных. Рассмотрим подробнее назначение каждого блока. По такой схеме построены практически все представители семейства MCS-51. Различные микросхемы этого семейства различаются только регистрами специального назначения (в том числе и количеством портов). Система команд всех контроллеров семейства MCS-51 содержит 111 базовых команд с форматом 1, 2 или 3 байта и не изменяется при переходе от одной микросхемы к другой. Это обеспечивает прекрасную переносимость программ с одной микросхемы на другую.

Блок управления и синхронизации (Timing and Control) предназначен для выработки синхронизирующих и управляющих сигналов, обеспечивающих координацию совместной работы блоков ОЭВМ во всех допустимых режимах ее работы. В состав блока управления входят:

- устройство формирования временных интервалов,

- комбинационная схема ввода-вывода,

- регистр команд,

- дешифратор команд.

Входные и выходные сигналы блока управления и синхронизации :

1 PSEN – разрешение программной памяти;

2 ALE – выходной сигнал разрешения фиксации адреса;

3 PROG – сигнал программирования;

4 EA – блокировка работы с внутренней памятью;

5 VPP – напряжение программирования;

6 RST – сигнал общего сброса.

Устройство формирования временных интервалов необходимо для синхронизации последовательности состояний ЦП, образующих машинный цикл, а также для правильной работы всех внутреннихзащелок и выходных буферов портов. Машинный цикл состоит из шести последовательныхсостояний (States) от S1 до S6, каждое из которых, в свою очередь, подразделяется на две фазы:

фазу 1 (Phase 1 - P1) и фазу 2 (Phase 2 - P2). Таким образом, машинный цикл может быть определен как последовательность временных интервалов S1P1, S1P2, S2P1,....,S6P2. Длительность фазы равна периоду следования тактовых импульсов, поэтому машинный цикл занимает 12 тактовых периодов.

Количество машинных циклов определяет продолжительность выполнения команд. Практически все команды выполняются за один или два машинных цикла, кроме команд умножения и деления, продолжительность выполнения которых составляет четыре машинных цикла. Логика ввода - вывода предназначена для приема и выдачи сигналов, обеспечивающих обмен информации с внешними устройствами через порты ввода вывода Р0-Р3.

Регистр команд предназначен для записи и хранения 8-ми разрядного кода операции выполняемой команды. Код операции, с помощью дешифратора команд и логики управления ЭВМ, преобразуется в микропрограмму выполнения команды.

Рис 2.3. Структурная схема однокристального микроконтроллера Intel 8051

(семейство MCS-51)

Арифметико-логическое устройство (ALU) представляет собой параллельное восьмиразрядное устройство, обеспечивающее выполнение арифметических и логических операций. АЛУ состоит из:

- регистров временного хранения -TMP1 и TMP2,

- ПЗУ констант,

- сумматора,

- дополнительного регистра - регистра В,

- аккумулятора - ACC,

- регистра слова состояния программ (регистр флагов)- PSW .

Регистры временного хранения TMP1, TMP2 - восьмиразрядные регистры, предназначенные для приема и хранения операндов на время выполнения операций над ними. Эти регистры программно не доступны.

ПЗУ констант обеспечивает выработку корректирующего кода при двоично-десятичном представлении данных, кода маски при битовых операциях и кода констант.

Параллельный восьмиразрядный сумматор представляет собой схему комбинационного типа с последовательным переносом, предназначенную для выполнения арифметических операций сложения, вычитания и логических операций сложения, умножения, неравнозначности и тождественности.

Регистр B - восьмиразрядный регистр, используемый во время операций умножения и деления. Для других инструкций он может рассматриваться как дополнительный сверхоперативный регистр.

Аккумулятор - восьмиразрядный регистр, предназначенный для приема и хранения результата, полученного при выполнении арифметико-логических операций или операций сдвига.

Регистр состояния программ PSW (Programm Status Word) предназначен для хранения слова состояния выполняемых команд. При выполнении многих команд в ALU формируется ряд признаков операции (флагов), которые фиксируются в регистре слова состояния программы (PSW). В табл. 1 приводится перечень флагов PSW, даются их символические имена и описываются условия их формирования.

Блок прерываний и последовательного интерфейса - UART(Universal Asynchronous Receiver/Transmitter) предназначен для организации ввода - вывода последовательных потоков информации и организации системы прерывания программ.По определению прерывание означает временное прекращение основного процесса вычислений для выполнения некоторых запланированных или незапланированных действий, вызываемых работой аппаратуры или программы.

Эти действия могут носить сервисный характер, быть запросами со стороны программы пользователя на выполнение обслуживания либо быть реакцией на нештатные ситуации.